ONFI(Open NAND Flash Interface)标准是由英特尔,镁光,海力士,台湾群联电子,SanDisk, 索尼,飞索半导体为首宣布统一制定的连接NAND闪存和控制芯片的接口标准,当初制定ONFI标准的主要目的是统一当时混乱的闪存标准。此IP是普通的输入接口,转换成ONFI接口,此IP常使用于FPGA和NAND flash通信的场景中。

根据ONFI总线的协议,把普通的接口数据在fpga内部寄存,并转化为符合ONFI协议的总线格式。

主要用于FPGA和NAND flash 之间进行通信,包括页读,页写,读取ID,擦除等。

无

端口的信号表如下表:

信号名字 | 位宽(bit) | 方向 | 说明 |

clk | 1 | I | 控制器的输入时钟信号 |

rst_n | 1 | I | 控制器的复位信号 |

up_sel | 1 | I | 控制器的片选信号 |

up_wr | 1 | I | 控制器的写信号高电平有效 |

up_addr | 14 | I | 控制器的地址总线 |

up_wdata | 32 | I | 控制器的写入的数据总线 |

up_rdata | 32 | O | 控制器的读出的数据总线 |

up_ack | 1 | O | 控制器的ack应答信号 |

ale | 1 | O | ONFI总线的地址锁存使能信号 |

ce_n | 2 | O | ONFI总线的片选使能信号 |

cle | 1 | O | ONFI总线的命令锁存信号 |

re_n | 1 | O | ONFI总线的读使能信号 |

we_n | 1 | O | ONFI总线的写使能信号 |

wp_n | 1 | O | ONFI总线的写保护信号 |

io8 | 8 | T | ONFI总线的输入输出总线 |

rb_n | 2 | I | ONFI总线的ready/busy指示信号 |

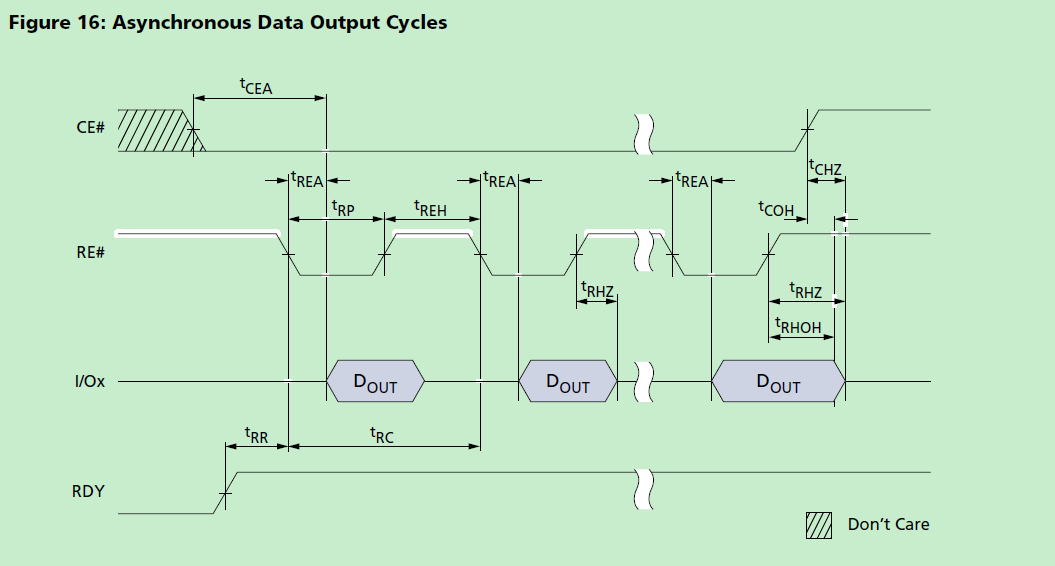

ONFI总线标准的时序图如下:

无

onfi onfi ( .clk ( s_axi_aclk ), .rst_n ( s_axi_aresetn ), .up_sel ( up_sel ), .up_wr ( up_wr ), .up_addr ( up_addr ), .up_wdata ( up_wdata ), .up_rdata ( up_rdata ), .up_ack ( up_ack ), .ale ( ale ), .ce_n ( ce_n ), .cle ( cle ), .re_n ( re_n ), .we_n ( we_n ), .wp_n ( wp_n ), .io8 ( io8 ), .rb_n ( rb_n )); |

通过在代码中,对顶层模块进行例化即能正常使用。参考代码可以详见NAND控制器IP。

好评率:100%

好评数量:0个

工作速度:5分

工作质量:5分

工作态度:5分

暂无评价

CPU/GPU ¥12000.00

CPU/GPU ¥25000.00

CPU/GPU ¥10000.00

CPU/GPU ¥30000.00

CPU/GPU ¥10000.00

CPU/GPU ¥15000.00

CPU/GPU ¥10000.00

CPU/GPU ¥10000.00

其他 ¥5000.00

其他 ¥5000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

FPGA电路 ¥10000.00

FPGA电路 ¥10000.00

模拟电路 ¥10000.00

模拟电路 ¥5000.00

模拟电路 ¥5000.00

模拟电路 ¥5000.00

模拟电路 ¥10000.00

模拟电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥15000.00

CPU/GPU ¥20000.00

CPU/GPU ¥18000.00

CPU/GPU ¥20000.00

其他 ¥10000.00

其他 ¥6000.00

其他 ¥2000.00

其他 ¥3000.00

其他 ¥12000.00

其他 ¥8000.00

FPGA电路 ¥5000.00

MCU电路 ¥4800.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

MCU电路 ¥50000.00

MCU电路 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥500000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00