此IP是AD7710芯片的控制器的源码,此模块的作用是把数据从AD7710芯片中读入到FPGA中。

根据芯片上的数据是否准备好的信号,如果数据准备好,就启动读操作,把准备好的数据读入到FPGA中,如果没有准备好,则等待数据准备好,直到数据准备好之后,然后把数据读入到FPGA中。

此IP是AD7710芯片的控制器的源码,此模块的作用是把数据从AD7710芯片中读入到FPGA中。

无

端口的信号表如下表:

信号名字 | 位宽(bit) | 方向 | 说明 |

clk | 1 | I | 控制器的输入时钟信号 |

rst_n | 1 | I | 控制器的复位信号 |

ch1dat | 23 | O | 芯片上通道1的数据 |

ch2dat | 23 | O | 芯片上通道2的数据 |

drdy_n | 1 | I | 芯片上数据准备好信号 |

a0 | 1 | O | 芯片上的a0信号 |

rfs_n | 1 | O | 芯片上的接受开始信号 |

tfs_n | 1 | O | 芯片上的发送开始信号 |

sclk | 1 | O | 芯片上的串行时钟信号 |

sdata | 1 | T | 芯片上的串行数据信号 |

sdoe | 1 | O | 串行数据输出时能信号 |

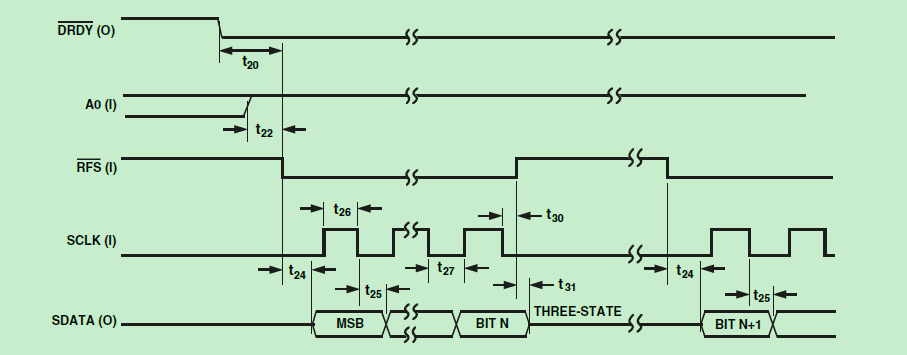

DATASHEET中的信号时序图如下图所示:

无

ctrl_top ctrl_top( .clk ( clk ) , .rst_n ( rst_n ) , .ch1dat( ch1dat ) , .ch2dat( ch2dat ) , .drdy_n( drdy_n ) , .a0 ( a0 ) , .rfs_n ( rfs_n ) , .tfs_n ( tfs_n ) , .sclk ( sclk ) , .sdata ( sdata ) , .sdoe ( sdoe ) ); |

通过在代码中,对顶层模块进行例化即能正常使用。

好评率:100%

好评数量:0个

工作速度:5分

工作质量:5分

工作态度:5分

暂无评价

CPU/GPU ¥12000.00

CPU/GPU ¥25000.00

CPU/GPU ¥10000.00

CPU/GPU ¥30000.00

CPU/GPU ¥10000.00

CPU/GPU ¥15000.00

CPU/GPU ¥10000.00

CPU/GPU ¥10000.00

其他 ¥5000.00

其他 ¥5000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

其他 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥10000.00

FPGA电路 ¥10000.00

FPGA电路 ¥10000.00

模拟电路 ¥10000.00

模拟电路 ¥5000.00

模拟电路 ¥5000.00

模拟电路 ¥5000.00

模拟电路 ¥10000.00

模拟电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

FPGA电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

DSP电路 ¥10000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥20000.00

CPU/GPU ¥15000.00

CPU/GPU ¥20000.00

CPU/GPU ¥18000.00

CPU/GPU ¥20000.00

其他 ¥10000.00

其他 ¥6000.00

其他 ¥2000.00

其他 ¥3000.00

其他 ¥12000.00

其他 ¥8000.00

FPGA电路 ¥5000.00

MCU电路 ¥4800.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

嵌入式 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

MCU电路 ¥50000.00

MCU电路 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥500000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00

其他 ¥50000.00